# DATA IMAGE CORPORATION

# **LCD Module Specification**

ITEM NO.: TG963220GRNNB-01

## **Table of Contents**

| 1.  | COVER & CONTENTS ·····            | 1  |

|-----|-----------------------------------|----|

| 2.  | REVISION HISTORY                  | 2  |

| 3.  | GENERAL SPECIFICATIONS ······     | 3  |

| 4.  | ABSOLUTE MAXIMUM RATINGS ·····    | 4  |

| 5.  | ELECTRICAL CHARACTERISTICS ······ | 5  |

| 6.  | ELECTRO-OPTICAL CHARACTERISTICS   | 5  |

| 7.  | TIMING CHARACTERISTICS ······     | 8  |

| 8.  | QUALITY ASSURANCE ·····           | 21 |

| 9.  | LOT NUMBERING SYSTEM ·····        | 24 |

| 10. | LCM NUMBERING SYSTEM ·····        | 24 |

| 11. | PRECAUTIONS IN USE LCM ······     | 25 |

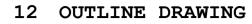

| 12. | OUTLINE DRAWING ·····             | 26 |

| 13. | PACKAGE INFORMATION               | 27 |

| R&D Dept. | Q.C. Dept.   | Eng. Dept.  | Prod. Dept.  |

|-----------|--------------|-------------|--------------|

|           |              |             |              |

|           |              |             |              |

| Version:  | Issued Date: | Sheet Code: | Total Pages: |

|           | 2002/8/19    |             | 27           |

| Rev | Date | Item | Page | Comment |

|-----|------|------|------|---------|

|     |      |      |      |         |

|     |      |      |      |         |

|     |      |      |      |         |

|     |      |      |      |         |

|     |      |      |      |         |

|     |      |      |      |         |

|     |      |      |      |         |

|     |      |      |      |         |

|     |      |      |      |         |

|     |      |      |      |         |

|     |      |      |      |         |

|     |      |      |      |         |

|     |      |      |      |         |

|     |      |      |      |         |

|     |      |      |      |         |

|     |      |      |      |         |

|     |      |      |      |         |

|     |      |      |      |         |

|     |      |      |      |         |

# 2. RECORD OF REVISION

Confidential Document

# 3. GENERAL SPECIFICATIONS

| Display Format :                             | 96 (\                                                | N) ×                 | 32 (H)     | Dots              |

|----------------------------------------------|------------------------------------------------------|----------------------|------------|-------------------|

| Dot Size :                                   | 0.3 (\                                               | N) ×                 | 0.33 (H)   | mm                |

| Dot Pitch                                    | 0.31 (\                                              | N) ×                 | 0.34 (H)   | mm                |

| View Area :                                  | 35 (\                                                | <b>N)</b> ×          | 13 (H)     | mm                |

| General Dimensions :                         | 39 (\                                                | <b>N)</b> ×          | 40.02 (H)  | × 2.2 (T) mm Max. |

| Weight :                                     | 10 g max.                                            |                      |            |                   |

| LCD Type :                                   | V STN Gray                                           | STI                  | N Yellow   | FSTN              |

| Polarizer mode :                             | VReflective                                          | Tra                  | nsflective |                   |

|                                              | Transmissive                                         | Ne                   | gative     |                   |

| View Angle :                                 | V6 O'clock                                           | 12                   | O'clock    | Others            |

| Backlight :                                  | LED                                                  | EL                   | [          | CCFL              |

| Backlight Color :                            | Yellow green                                         | Am                   | ber        | Blue Green        |

|                                              | White                                                | Oth                  | iers       |                   |

| Controller / Driver :<br>Temperature Range : | SED1530TAA<br>Normal<br>Operating 0 t<br>Storage -20 | :o 50°C<br>0 to 70°( | Opera      | •                 |

# 4. ABSOLUTE MAXIMUM RATINGS

|                                |         |         | Vss=    | 0V, Ta = 23 | 5°C |

|--------------------------------|---------|---------|---------|-------------|-----|

| Item                           | Symbol  | Min.    | Max.    | Unit        |     |

| Supply Voltage<br>(Logic)      | VDD-VSS | 0       | 8       | V           |     |

| Supply Voltage<br>(LCD Driver) | VDD-VEE | 0       | 16.5    | V           |     |

| Input Voltage                  | Vi      | VSS-0.3 | VDD+0.3 | V           |     |

| Operating Temperature          | Тор     | -20     | 70      | °C          |     |

| Storage Temperature            | Тѕтс    | -30     | 80      | °C          |     |

## 4.1 ELECTRICAL ABSOLUTE MAXIMUM RATINGS

### 4.2 ENVIRONMENTAL ABSOLUTE MAXIMUM RATINGS

| Item         | Oper   | rating               | Sto                 | orage                | Comment              |  |

|--------------|--------|----------------------|---------------------|----------------------|----------------------|--|

| llem         | (Min.) | Max.)                | (Min.)              | (Max.)               | Comment              |  |

| Ambient Temp | -20    | 70                   | -30                 | 80                   | Note (1)             |  |

| Humidity     | Note   | e (2)                | Note(2)             |                      | Without Condensation |  |

| Vibration    |        | 4.9M/S <sup>2</sup>  |                     | 19.6M/S <sup>2</sup> | XYZ Direction        |  |

| Shock        |        | 29.4M/S <sup>2</sup> | 490M/S <sup>2</sup> |                      | XYZ Direction        |  |

Note(1) Ta =  $0^{\circ}C$  : 50Hr Max.

Note(2) Ta  $\leq 40^{\circ}$ C : 90% RH Max.

Ta  $\geq 40^{\circ}$ C : Absolute humidity must be lower than the humidity of 90% RH at 40°C.

Confidential Document

| Item                      | Symbol                | Condition | Min.    | Тур. | Max.    | Unit |

|---------------------------|-----------------------|-----------|---------|------|---------|------|

| Supply Voltage<br>(Logic) | VDD-VSS               |           | 2.7     | 3.3  | 5.5     | V    |

| Supply Voltage<br>(LCD)   | ge <sub>VDD-VEE</sub> | 0°C       | 5.2     | 5.5  | 5.8     |      |

|                           |                       | 25°C      | 4.7     | 5.0  | 5.3     | V    |

|                           |                       | 50°C      | 4.2     | 4.5  | 4.8     |      |

| Input Valtage             | Vін                   |           | VSS+2.0 |      | Vdd     | v    |

| Input Voltage             | VIL                   |           | Vss     |      | VSS+0.8 | v    |

| Logic Supply<br>Current   | IDD                   |           |         | 0.7  |         | mA   |

# 5. ELECTRICAL CHARACTERISTICS

# 6. ELECTRO-OPTICAL CHARACTERISTICS

| ITEM            | Symbol         | Condition | Min. | Тур. | Max. | Unit   | Ref.     |  |

|-----------------|----------------|-----------|------|------|------|--------|----------|--|

| Rise Time       | Tr             | 0°C       |      |      |      | me     |          |  |

|                 | 11             | 25°C      |      | 130  | 260  | ms     |          |  |

|                 | Tf             | 0°C       |      |      |      | me     | Note (1) |  |

| Fall Time       | 11             | 25°C      |      | 180  | 360  | ms     |          |  |

| Contrast        | CR             | 25°C      | 2    | 5    |      |        | Note (3) |  |

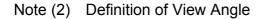

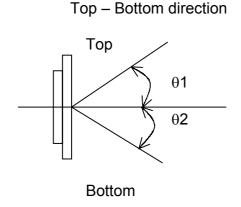

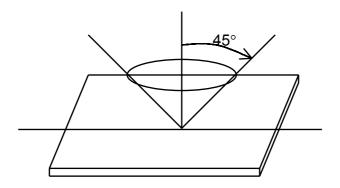

| View Angle      | θ1~θ2          | 25°C &    | 60   |      |      | Degree | Note (2) |  |

| View Angle      | Ø1, Ø <b>2</b> | CR≥2      | 90   |      |      | Degree | Note (2) |  |

| Frame Frequency | Ff             | 25°C      |      | 70   |      | Hz     |          |  |

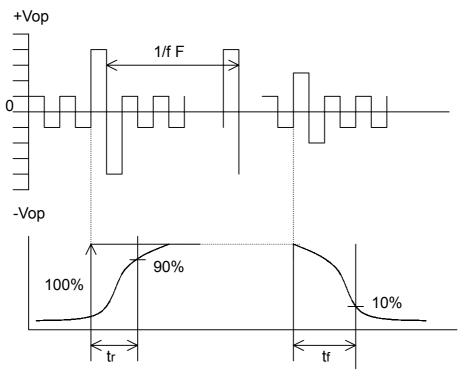

Note (1) & (2) : See next page

Note (3) : Contrast ratio is defined under the following condition:

CR= Brightness of non-selected condition Brightness of selected condition

- (a). Temperature ----- 25°C

- (b). Frame frequency ---- 70Hz

- (c). Viewing angle -----  $\theta = 0^{\circ}$ ,  $\emptyset = 0^{\circ}$

- (d). Operating voltage --- 5.0V

Note (1) Response time is measured as the shortest period of time possible between the change in state of an LCD segment as demonstrated below:

Condition:

- (a). Temperature -----25°C

- (b). Frame frequency ----- 70Hz

- (c). View Angle -----  $\theta = 0^\circ, \emptyset = 0^\circ$

- (d). Operating voltage ----- 5.0V

**Right -- Left direction**

Page: 6/27

# 7. TIMING CHARACTERISTICS

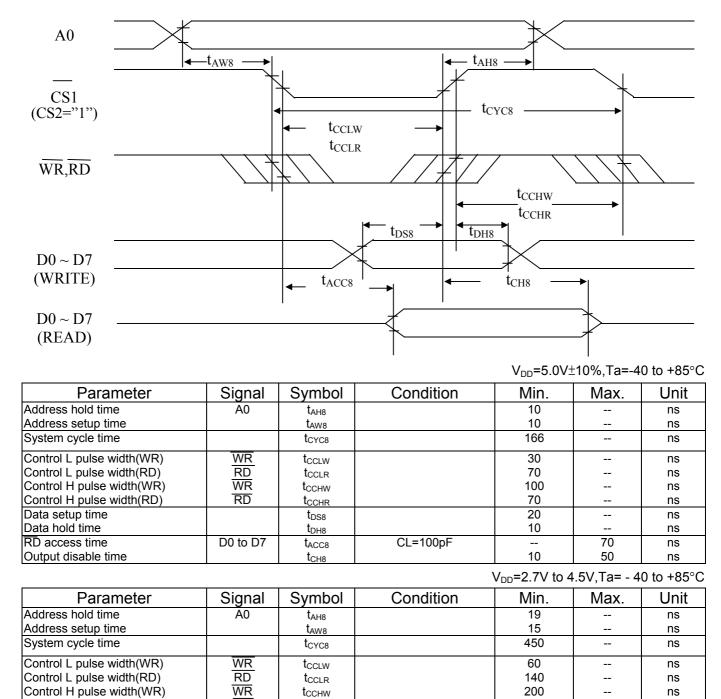

### AC Characteristics

(1)System buses

Read/write characteristics I (8080series microprocessor)

Output disable time 10 100 t<sub>CH8</sub> Notes:1. The input signal rise/fall time (t<sub>r</sub>,t<sub>f</sub>) is specified at 15 ns or less. When system cycle time is used at a high speed, it is specified by t<sub>r</sub>+t<sub>f</sub> ≤  $(t_{CYC8} - t_{CCLW})$  or  $t_r + t_f \leq (t_{CYC8} - t_{CCLR} - t_{CCHR})$ .

CL=100pF

**t**<sub>CCHR</sub>

t<sub>DS8</sub>

t<sub>DH8</sub>

t<sub>ACC8</sub>

Control H pulse width (RD)

Data setup time

Data hold time

RD access time

2. Every timing is specified on the basis of 20% and 80% of  $V_{DD}$ . 3.  $t_{EWHR}$  and  $t_{EWHW}$  are specified by the overlap period in which CS1 is "0"(CS="1") and WR and RD are"0".

RD

D0 to D7

ns

ns

ns

ns

ns

---

140

140

40

15

\_\_\_

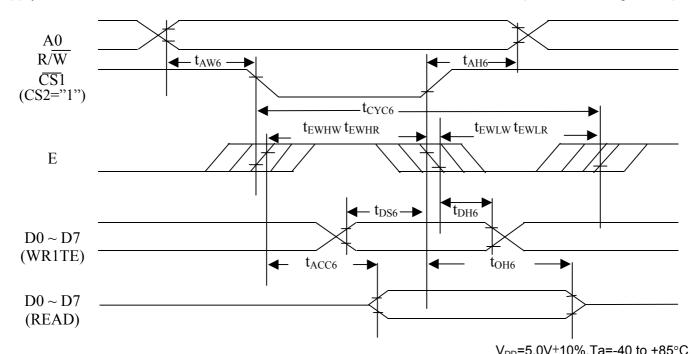

(2)System buses

Read/write characteristics II (6800-series microprocessor)

Signal Symbol Condition Parameter Min. Max. Unit System cycle time 166 t<sub>CYC6</sub> --ns Address hold time 10 A0 t<sub>AH6</sub> ns ---W/R Address setup time 10 ns t<sub>AW6</sub> Data setup time 20 t<sub>DS6</sub> ns --Data hold time 10  $t_{\rm DH6}$ \_\_\_ ns D0 to D7 Output disable time CL=100pF 10 50 t<sub>OH6</sub> ns Access time  $t_{ACC6}$ 70 ns ---70 Enable READ ns --t<sub>EWHR</sub> Е Low pulse width WRITE 30 ns --t<sub>EWHW</sub> Enable READ 70 -ns t<sub>EWLR</sub> Е High pulse width WRITE 100 ns --t<sub>EWLW</sub>

| / <sub>DD</sub> -5.0V | 10%,1a4 | 10 10 | +00 | U |

|-----------------------|---------|-------|-----|---|

|                       |         |       |     |   |

|                                   |       |            |                                      |           | V <sub>DD</sub> =2.7V to | 4.5V,Ta=-4 | 0 to +85°C |

|-----------------------------------|-------|------------|--------------------------------------|-----------|--------------------------|------------|------------|

| Paramete                          | r     | Signal     | Symbol                               | Condition | Min.                     | Max.       | Unit       |

| System cycle time                 |       |            | t <sub>CYC6</sub>                    |           | 450                      |            | ns         |

| Address hold time                 |       | A0<br>R/ W | t <sub>AW6</sub>                     |           | 15                       |            | ns         |

| Address setup time                |       | R/ W       | t <sub>AH6</sub>                     |           | 19                       |            | ns         |

| Data setup time<br>Data hold time |       | D0 to D7   | t <sub>DS6</sub><br>t <sub>DH6</sub> |           | 40<br>15                 |            | ns<br>ns   |

| Output disable time               |       | D0 10 D7   | t <sub>OH6</sub>                     | CL=100pF  | 10                       | 100        | ns         |

| Access time                       |       |            | t <sub>ACC6</sub>                    |           |                          | 140        | ns         |

| Enable                            | READ  | E          | t <sub>EWHR</sub>                    |           | 140                      |            | ns         |

| Low pulse width                   | WRITE | L          | $t_{\rm EWHW}$                       |           | 60                       |            | ns         |

| Enable                            | READ  | E          | t <sub>EWLR</sub>                    |           | 140                      |            | ns         |

| High pulse width                  | WRITE |            | t <sub>EWLW</sub>                    |           | 200                      |            | ns         |

Notes:1. The input signal rise/fall time (t, tr) is specified at 15 ns or less. When system cycle time is used at a high speed, it is specified by  $t_r+t_f \leq (t_{CYC6} - t_{EWLW} - t_{EWHW}) \text{ or } t_r+t_f \leq (t_{CYC6} - t_{EWLR} - t_{EWHR}).$

2.Every timing is specified on the basis of 20% and 80% of  $V_{DD}$ . 3.  $t_{EWHR}$  and  $t_{EWHW}$  are specified by the overlap period in which CS1 is "0"(CS2="1") and E is "1".

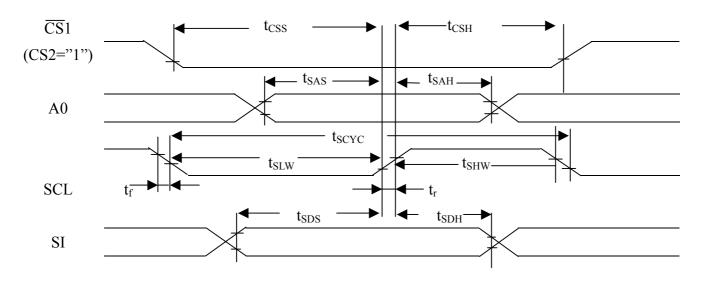

## (3)System buses

V<sub>DD</sub>=5.0V±10%,Ta=-40 to +85°C

| Parameter                  | Signal | Symbol           | Condition | Min. | Max. | Unit |

|----------------------------|--------|------------------|-----------|------|------|------|

| System clock cycle         |        | tscyc            |           | 250  |      | ns   |

| System clock H pulse width | SCL    | t <sub>SHW</sub> |           | 100  |      | ns   |

| System clock L pulse width |        | t <sub>SLW</sub> |           | 75   |      | ns   |

| Address setup time         | A0     | t <sub>SAS</sub> |           | 50   |      | ns   |

| Address hold time          | AU     | t <sub>SAH</sub> |           | 200  |      | ns   |

| Data setup time            | SI     | t <sub>SDS</sub> |           | 50   |      | ns   |

| Data hold time             | 31     | t <sub>SDH</sub> |           | 50   |      | ns   |

| CS serial clock time       | CS     | t <sub>css</sub> |           | 30   |      | ns   |

|                            | 63     | t <sub>CSH</sub> |           | 100  |      |      |

| $V_{DD}=2.7V$ | to 4.5V | ,Ta=-40 | to | +85° | С |

|---------------|---------|---------|----|------|---|

|---------------|---------|---------|----|------|---|

| Parameter                  | Signal | Symbol            | Condition | Min. | Max. | Unit |

|----------------------------|--------|-------------------|-----------|------|------|------|

| System clock cycle         |        | t <sub>scyc</sub> |           | 500  |      | ns   |

| System clock H pulse width | SCL    | t <sub>SHW</sub>  |           | 200  |      | ns   |

| System clock L pulse width |        | t <sub>SLW</sub>  |           | 150  |      | ns   |

| Address setup time         | A0     | t <sub>SAS</sub>  |           | 100  |      | ns   |

| Address hold time          | AU     | t <sub>SAH</sub>  |           | 400  |      | ns   |

| Data setup time            | SI     | t <sub>SDS</sub>  |           | 100  |      | ns   |

| Data hold time             | 51     | t <sub>SDH</sub>  |           | 100  |      | ns   |

| CS serial clock time       | CS     | t <sub>css</sub>  |           | 60   |      | ns   |

|                            | 0.5    | t <sub>CSH</sub>  |           | 200  |      |      |

Notes:1.The input signal rise and fall times must be within 15 nanoseconds. 2.All signal timings are limited based on 20% and 80% of V<sub>DD</sub> voltage.

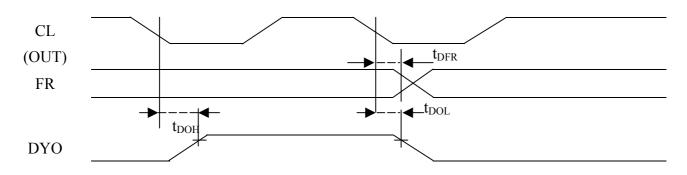

### (4) Display control timing

### **Output timing**

#### V<sub>DD</sub>=5.0V ±10%,Ta=-40 to +85°C

| - <b>-</b>         |        |                  |           | 00   | , - |      |      |

|--------------------|--------|------------------|-----------|------|-----|------|------|

| Parameter          | Signal | Symbol           | Condition | Min. | Тур | Max. | Unit |

| FR delay time      | FR     | t <sub>DFR</sub> | C∟=50pF   |      | 10  | 40   | ns   |

| DYO "H" delay time | DYO    | t <sub>DOH</sub> |           |      | 40  | 100  | ns   |

| DYO "L" delay time |        | t <sub>DOL</sub> |           |      | 40  | 100  | ns   |

#### $V_{SS}=0V, V_{DD}=2.7V 4.5V, Ta=to 40 to +85^{\circ}C$ **Output timing** Dara Signal Symbol Condition ator

| Parameter          | Signal | Symbol           | Condition | тур    | wax. | υπι |

|--------------------|--------|------------------|-----------|--------|------|-----|

| FR delay time      | FR     | t <sub>DFR</sub> | C∟=50pF   | <br>15 | 80   | ns  |

| DYO "H" delay time | DYO    | t <sub>DOH</sub> |           | <br>70 | 200  | ns  |

| DYO "L" delay time |        | t <sub>DOL</sub> |           | <br>70 | 200  | ns  |

Notes:1.The output timing is valid in master mode. 2.Every timing is specified on the basis of 20% and 80% of V<sub>DD</sub>.

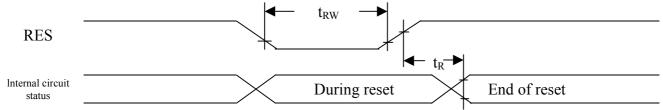

### (5) Reset timing

V<sub>DD</sub>=5.0V ±10%,Ta=-40 to +85°C

| Parameter             | Signal | Symbol          | Condition | Min. | Тур | Max. | Unit    |

|-----------------------|--------|-----------------|-----------|------|-----|------|---------|

| Reset time            |        | t <sub>R</sub>  |           | 0.5  |     |      | $\mu$ S |

| Reset low pulse width | RES    | t <sub>RW</sub> |           | 0.5  |     |      | $\mu$ S |

#### V<sub>DD</sub>=2.7V to 4.5V,Ta=-40 to +85°C

| Parameter             | Signal | Symbol          | Condition | Min. | Тур | Max. | Unit        |

|-----------------------|--------|-----------------|-----------|------|-----|------|-------------|

| Reset time            |        | t <sub>R</sub>  |           | 1.0  |     |      | $\mu{ m s}$ |

| Reset low pulse width | RES    | t <sub>RW</sub> |           | 1.0  |     |      | $\mu{ m S}$ |

Notes:1.The reset timing is specified on the basis of 20% and 80% of  $V_{\text{DD}}$ .

# 7.1. PIN DESCRIPTON

# **Power Supply**

| Name                                                                               | I/O    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                              | Number of pins |

|------------------------------------------------------------------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| V <sub>DD</sub>                                                                    | Supply | +5V power supply. Connect to microprocessor power supply pin V <sub>CC</sub> .                                                                                                                                                                                                                                                                                                                                                                           | 2              |

| V <sub>SS</sub>                                                                    | Supply | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1              |

| V <sub>1</sub> ,V <sub>2</sub><br>V <sub>3</sub> ,V <sub>4</sub><br>V <sub>5</sub> | Supply | LCD driver supply voltages. The voltage determined by LCD cell is impedance-converted by a resistive driver or an operational amplifier for application. Voltages should be the following relationship: $V_{DD} \ge V_1 \ge V_2 \ge V_3 \ge V_4 \ge V_5$<br>When the 0n-chip operating power circuit is on, the following voltages are given to $V_1$ to $V_4$ by the on-chip power circuit. Voltage selection is performed by the Set LCD Bias command. | 6              |

|                                                                                    |        | SED 1530           V1         1/5 • V5         1/6 • V5           V2         2/5 • V5         2/6 • V5           V3         3/5 • V5         4/6 • V5           V4         4/5 • V5         5/6 • V5                                                                                                                                                                                                                                                     |                |

### **LCD Driver Supplies**

| Name             | I/O | Description                                                                                                      | Number of pins |

|------------------|-----|------------------------------------------------------------------------------------------------------------------|----------------|

| CAP1+            | 0   | DC/DC voltage converter capacitor 1 positive connection                                                          | 1              |

| CAP1-            | 0   | DC/DC voltage converter capacitor 1 negative connection                                                          | 1              |

| CAP2+            | 0   | DC/DC voltage converter capacitor 2 positive connection                                                          | 1              |

| CAP2-            | 0   | DC/DC voltage converter capacitor 2 negative connection                                                          | 1              |

| CAP3-            | 0   | DC/DC voltage converter capacitor 1 negative connection                                                          | 1              |

| V <sub>OUT</sub> | 0   | DC/DC voltage converter output                                                                                   | 1              |

| VR               | I   | Voltage adjustment pin. Applies voltage between $V_{\mbox{\scriptsize DD}}$ and $V_5$ using a resistive divider. | 1              |

## Microprocessor Interface

| Name          | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                | Number of pins |

|---------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| D0 to D7      | I/O | 8-bit bi-directional data bus to be connected to the standard 8-bit or 16-bit                                                                                                                                                                                                                                                                                                                              | 8              |

| (SI)<br>(SCL) |     | microprocessor data bus.<br>When the serial interface selects;<br>D7:Serial data input(SI)<br>D6:Serial clock input (SCL)                                                                                                                                                                                                                                                                                  |                |

| A0            | Ι   | Control/display data flag input. It is connected to the LSB of micro-<br>processor address bus. When low, the data on D0 to D7 is control data.<br>When high, the data on D0 to D7 is display data.                                                                                                                                                                                                        | 1              |

| RES           |     | When $\overline{\text{RES}}$ is caused to go low, initialization is executed.<br>A reset operation is performed at the $\overline{\text{RES}}$ signal level.                                                                                                                                                                                                                                               | 1              |

| CS1<br>CS2    | Ι   | Chip select input. Data input/output is enabled when-CS1 is low and CS2 is high. When chip select is non-active, D0 to D7 will be "HZ".                                                                                                                                                                                                                                                                    | 2              |

| RD<br>(E)     | -   | <ul> <li>When interfacing to an 8080 series microprocessor:<br/>Active low. This input connects the RD signal of the 8080 series<br/>microprocessor . While this signal is low, the SED1530 series data<br/>bus output is enabled.</li> <li>When interfacing to a 6800 series microprocessor:<br/>Active high. This is used as an enable clock input pin of the 6800 series<br/>microprocessor.</li> </ul> | 1              |

| WR<br>(R/W)   | Ι   | <ul> <li>Write enable input. When interfacing to an 8080-series microprocessor,<br/>WR is active low.</li> <li>When interfacing to an 6800-series microprocessor,<br/>it will be read mode when R/W is high and it will be write mode when<br/>R/W is low.<br/>R/W= "1" :Read<br/>R/W= "0" :Write</li> </ul>                                                                                               | 1              |

| Name | I/O |           | Description                                                                                                                                  |                                     |       |            |               |  |  |  |

|------|-----|-----------|----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|-------|------------|---------------|--|--|--|

| C86  | Ι   | C86=hi    | Microprocessor interface select terminal.<br>C86=high: 6800 series microprocessor interface<br>C86=low: 8080 series microprocessor interface |                                     |       |            |               |  |  |  |

| P/S  | Ι   | Serial of | Serial data input/parallel data input select pin.                                                                                            |                                     |       |            |               |  |  |  |

|      |     | P/S       | Chip select                                                                                                                                  | Data/command                        | Data  | Read/write | Serial clock  |  |  |  |

|      |     | "H"       | CS1,CS2                                                                                                                                      | A0                                  | D0-D7 | RD,WR      |               |  |  |  |

|      |     | "L"       | CS1,CS2                                                                                                                                      | A0                                  | SI    | Write only | SCL(D6)       |  |  |  |

|      |     |           | P/S= low, D0                                                                                                                                 | lata can be read<br>to D5 are HZ ar |       |            | be fixed high |  |  |  |

# 7.2. LCD Driver Outputs

| Name | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                         | Number of pins |

|------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| M/S  | I   | SED1530 series master/slave mode select input. When a necessary<br>signal is output to the LCD, the master operation is synchronized with<br>the LCD system, while when a necessary signal is input to the LCD,<br>the slave operation is synchronized with the LCD system.<br>M/S= high : Master operation<br>M/S= low : Slave operation<br>The following is provided depending on the M/S status. | 1              |

|      |     | Model         Status         OSC<br>circuit         Power<br>supply<br>circuit         CL         FR         DYO         FRS         DOF                                                                                                                                                                                                                                                            |                |

|      |     | SED153*D**         Master         Enabled         Enabled         Output         Output         Output         Output         Output           SED153*D**         Master         Enabled         Disabled         Input         Input         HZ         HZ         Input                                                                                                                           |                |

| CL   | I/O | Display Clock input/output. When the SED1530 series selects Master/<br>slave mode, each CL pin is connected. When it is used in<br>combination with the common driver, this input/output is connected to<br>common driver YSCL pin.<br>M/S= high: Output<br>M/S= low: input                                                                                                                         | 1              |

| FR   | I/O | LCD AC signal input/output. When the SED1530 series selects master/<br>slave mode, each FR pin is connected.<br>When the SED1530 series selects master mode this input/output is<br>connected to the common driver FR pin.<br>M/S= high: Output<br>M/S= low: input                                                                                                                                  | 1              |

| DYO  | I/O | Common drive signal output. This output is enabled for only at master operation and connects to the common driver DIO pin. It becomes HZ at slave operation.                                                                                                                                                                                                                                        | 1              |

| VS1  | 0   | Internal power supply voltage monitor output.                                                                                                                                                                                                                                                                                                                                                       | 1              |

| DOF  | I/O | LCD blanking control input/output. When the SED1530 series selects master/slave mode, the respective DOF pin is connected. When it is used in combination with the common <u>driver</u> (SED1635), this output/ input is connected to the common driver DOFF pin.<br>M/S= high: Output<br>M/S= low: input                                                                                           | 1              |

| FRS  | 0   | Static drive output.<br>This is enabled only at master operation and used together with the FR<br>pin. This output becomes HZ at slave operation.                                                                                                                                                                                                                                                   | 1              |

| Name          | I/O |                       |                        |          | Descripti                                             | on                                     | Nu | mber of pins |

|---------------|-----|-----------------------|------------------------|----------|-------------------------------------------------------|----------------------------------------|----|--------------|

| On<br>(SEG n) | 0   | LCD driv<br>the mod   |                        | ollowing | g assignment is ma                                    | de depending on                        |    | •            |

| (Com n)       |     |                       | -                      |          |                                                       | 1                                      | -  |              |

|               |     |                       |                        |          | SEG                                                   | COM                                    | _  |              |

|               |     |                       | SED 1530E              |          | 00~099                                                | O100~O131                              | _  |              |

|               |     |                       | SED 1530E<br>SED 1530E | 1        |                                                       |                                        |    |              |

|               |     | SEG out               |                        |          |                                                       |                                        |    |              |

|               |     | V <sub>5</sub> levels | s is selected by o     |          |                                                       |                                        |    |              |

|               |     | and FR                |                        |          |                                                       |                                        |    |              |

|               |     |                       | RAM data               | FR       | On outpu                                              | it voltage                             |    |              |

|               |     |                       |                        |          | Normal display                                        | Reverse display                        |    |              |

|               |     |                       | Н                      | Н        | V <sub>DD</sub>                                       | V <sub>2</sub>                         |    |              |

|               |     |                       |                        | L        | V <sub>5</sub>                                        | V <sub>3</sub>                         |    |              |

|               |     |                       | 0                      | Н        | V <sub>2</sub>                                        | V <sub>DD</sub>                        |    |              |

|               |     |                       |                        | L        | V <sub>3</sub>                                        | V <sub>5</sub>                         |    |              |

|               |     |                       | Power save             |          | V                                                     | DC                                     |    |              |

|               |     |                       | •                      |          | ve output. One of \<br>on of scan data an             | d FR signal.                           |    |              |

|               |     |                       | Scan data              |          | FR On output                                          | voltage                                |    |              |

|               |     |                       | Н                      |          | H V <sub>5</sub>                                      |                                        |    |              |

|               |     |                       |                        |          | L V <sub>DD</sub>                                     |                                        |    |              |

|               |     |                       | L                      |          | H V <sub>1</sub>                                      |                                        |    |              |

|               |     |                       | Power save             |          | L V <sub>4</sub>                                      |                                        |    |              |

|               |     |                       | Fower save             |          | V <sub>DD</sub>                                       |                                        |    |              |

| COMS          | 0   | Effectiv              |                        | SED15    | t is not used, it is r<br>30,SED1532,SED <sup>2</sup> | nade open.<br>1533 and SED1534         |    |              |

|               |     | When I<br>SED15       | multiple numbers       | s of the | SED1530,SED15<br>COMS signal is or                    | 32,SED1533 and<br>utput to both master |    |              |

|               |     |                       |                        |          |                                                       |                                        |    |              |

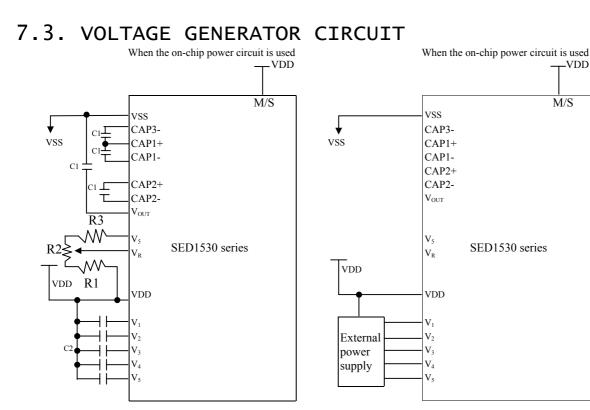

Reference setup value: SED1530 V<sub>5</sub>≒-7 to -9V SED1531 V<sub>5</sub> $\equiv$ -11 to -13V (variable) SED1532 V<sub>5</sub> = -11 to -13V (variable)

|                     | 5ED1552     | $v_5 = -11 \text{ to } -13$ | v (variable) |

|---------------------|-------------|-----------------------------|--------------|

|                     | SED1530     | SED1531                     | SED1532      |

| C1                  | 1.0~4.7ufΩ  | 1.0~4.7uF                   | 1.0~4.7uF    |

| C2                  | 0.22~0.47uf | 0.47~1.0uf                  | 0.47~1.0uf   |

| R1                  | 700 K Ω     | $1 M \Omega$                | $1 M \Omega$ |

| R2                  | 200 Κ Ω     | 200 Κ Ω                     | 200 Κ Ω      |

| R3                  | 1.6MΩ       | $4 M \Omega$                | $4 M \Omega$ |

| LCD<br>SIZE         | 16x50mm     | 32x64mm                     | 32x100mm     |

| DOT<br>CONFIGURATON | 32x100      | 64x128                      | 64x200       |

\*1: As the input impedance of VR is high, a noise protection using short wire and cable shied is required.

\*2: C1 and C2 depend on the capacity of the LCD panel to be driven. Seta value so that the LCD drive voltage may be stable.

[Setup example]

Turn on the voltage regulator and voltage follower and give an external voltage to VOUT. Display a horizontal-stripe LCD heavy load pattern and determine C2 so that the LCD drive voltage (V1 to V5) may be stable. However, the capacity value of C2 must be all equal. Next, turn on all the on-board power supplies and determine C1.

\*3:LCD SIZE means the length and breadth of the display portion of the LCD panel.

### When the RES input goes low, this LSI is initialized. Initialized status 1.Display OFF 2.Normal display

**Reset Circuit**

3.ADC select: Normal display (ADC command D0=low)

VDD

M/S

- 4.Read modify write OFF 5.Power control register (D2, D1, D0)=(0,0,0)

- 6.Register data clear in serial interface

- 7.LCD power supply bias ratio 1/6(SED1530),

- 1/8(SED1531, SED1532)

- 8.static indicator: OFF

- 9.Display start line register set at line 1 10.Column address counter set at address 0

- 11. Page address register set at page 0

- 12.Output status register (D3)=(0)

- 13. Electronic control register set at 0 14. Test command OFF

As seen in Microprocessor Interface (Reference Example), connect The RES pin to the reset pin of the microprocessor and initialize the microprocessor at the same time.

In case the SED1530 series does not use the internal LCD power Supply circuit, the RES must be low when the external LCD power Supply is turned on.

When  $\overline{\text{RES}}$  goes low, each register is cleared and set to the above Initialized status. However, it has no effect on the oscillator circuit And output pins ( FR, CL, DYO, D0 to D7). The initialization by RES pin signal is always required during Power-on. If the control signal from the MPU is HZ, an over current May flow through the IC. A protection is required to prevent the HZ Signal at the input pin during power-on.

Be sure to initialize it by  $\overline{\text{RES}}$  pin when turning on the power supply. When the reset command is used, only parameters 8 to 14 in the Above initialization are executed

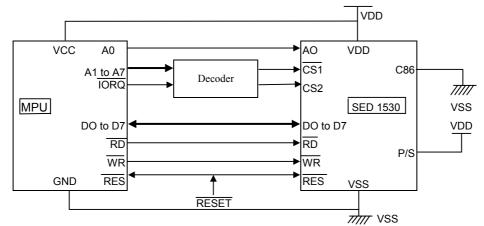

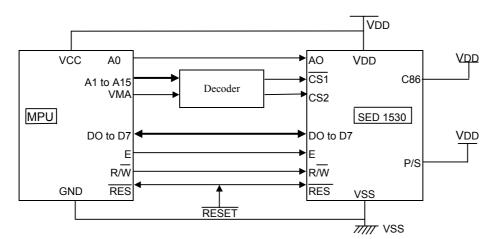

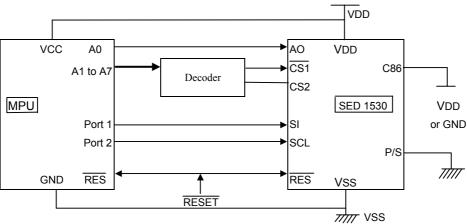

# 7.4. MICROPROCESSOR INTERFACE (Reference example)

The SED1530 series chips directly connect to 8080 and 6800-series microprocessors. Also serial interfacing requires less signal lines between them. When multiple chips are used in the SED 1530 series they can be connected to the microprocessor and one of them can be selected by Chip Select.

### 8080-series microprocessors

6800-series microprocessors

serial interface

# 7.5 FUNCTIONAL DESCRIPTION

### **Microprocessor Interface**

### Interface type selection

The SED1530 series can transfer data via 8-bit bi-directional data buses (D7 to D0) or via serial data input (SI). When high or low is selected for the polarity of P/S pin, either8-bit parallel data input or serial data input can be selected as shown in Table 1. When serial data input is selected, RAM data cannot be read out.

| P/S | Туре           | CS1 | CS2 | A0 | RD | WR | C86 | D7         | D6         | D0 to D5     |

|-----|----------------|-----|-----|----|----|----|-----|------------|------------|--------------|

| Н   | Parallel input | CS1 | CS2 | A0 | RD | WR | C86 | D7         | D6         | D0 to D5     |

| L   | Serial input   | CS1 | CS2 | A0 | -  | -  | -   | SI         | SCL        | (HZ)         |

|     |                |     |     |    |    |    |     | "-" must a | lways be h | high or low. |

Table 1

Parallel input

When the SED1530 series selects parallel input(P/S= high), the 8080 series microprocessor or 6800 series microprocessor can be selected by causing the C86 pin to go high or low as shown in Table2.

|     |                                               |     |     |    | Table2 |     |          |

|-----|-----------------------------------------------|-----|-----|----|--------|-----|----------|

| C86 | Туре                                          | CS1 | CS2 | A0 | RD     | WR  | D0 to D7 |

| Н   | 6800 micro-                                   | CS1 | CS2 | A0 | E      | R/W | D0 to D7 |

| L   | processor bus<br>8080 micro-<br>processor bus | CS1 | CS2 | A0 | RD     | R/W | D0 to D7 |

### **Data Bus Signals**

The SED1530 series identifies the data bus signal according to A0,E,R/W, (RD, WR) signals.

|        |                |                | Table3 |                                                     |

|--------|----------------|----------------|--------|-----------------------------------------------------|

| Common | 6800 processor | 8080 processor |        | Function                                            |

| A0     | (R/W)          | RD             | WR     | Function                                            |

| 1      | 1              | 0              | 1      | Reads display data.                                 |

| 1      | 0              | 1              | 0      | Writes display data.                                |

| 0      | 1              | 0              | 1      | Reads status.                                       |

| 0      | 0              | 1              | 0      | Writes control data in internal register. (Command) |

#### Serial Interface (P/S is low)

The aerial interface consists of an 8-bit shift register and a 3-bit counter. The serial data input and serial clock input are enabled when CS1 is low and CS2 is high (in chip select status). When chip is not selected, the shift register and counter are rest.

Serial data of D7,D6,...,D0 is read at D7 in this sequence when serial clock (SCL) goes high. They are converted Into 8-bit parallel data and processed on rising edge of every eighth serial clock signal. The serial data input (SI) is determined to be the display data when A0 is high, and it is control data when A0 is low A0 is read on rising edge

of every eighth clock signal.

Figure 1 shows a timing chart of serial interface signals. The serial clock signal must be terminated correctly against termination reflection and ambient noise. Operation checkout on the actual machine is recommended.

| CS1 |                                                                                                                                                   |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------|

| CS2 |                                                                                                                                                   |

| SI  | D7         D6         D5         D4         D3         D2         D1         D0         D7         D6         D5         D4         D2         D1 |

| SCL |                                                                                                                                                   |

| A0  | Figure 1                                                                                                                                          |

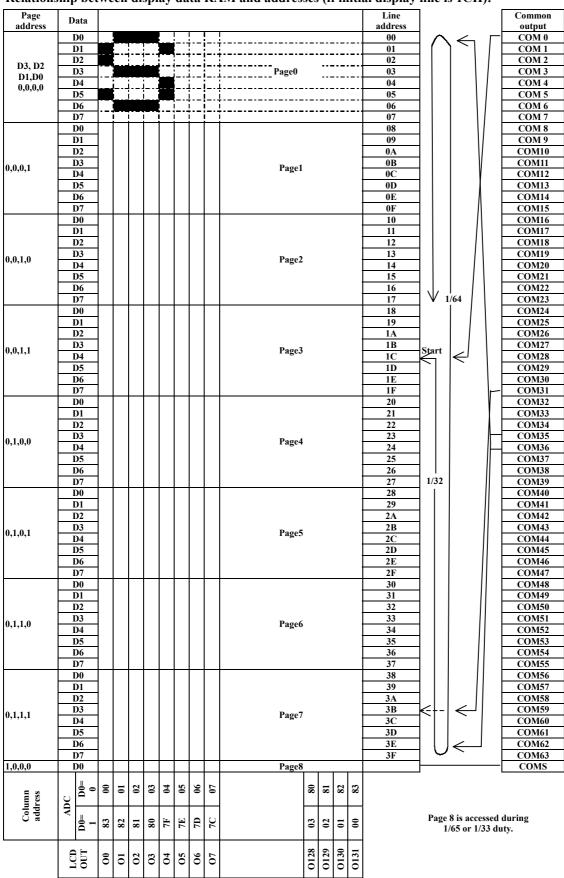

# 7.6. Column Address Counter

This is a 8bit presettable counter that provides column address to the display RAM(refer to Figure 4). It is incremented by 1 when a Read/write command is entered. However, the counter is not incremented but locked if a non-existing address above 84H is specified. It is unlocked when a column address is set again. The Column Address counter is independent of Page Address register. When ADC Select command is issued to display inverse display, the Column address decoder inverts the relationship between RAM Column address and display segment output.

#### Page Address Register

This is a 4-bit page address register that provides page address to the display RAM (refer to Figure 4). The microprocessor issues Set Page Address command to change the page and access to another Page. Page address 8 (D3 is high, but D2, D1 and D0 are low) is

RAM area dedicate to the indicator, and display data D0 is only valid.

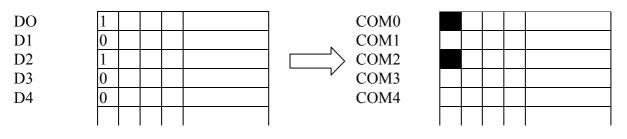

#### Display Data RAM

The display data RAM stores pixel data for LCD. It is a 65column by 132-row(8-page by 8 bit+1) addressable array. Each pixel can be selected when page and column addresses are specified. The time required to transfer data is very short because the microprocessor enters D0 to D7 corresponding to LCD common lines as shown in Figure 3. Therefore, multiple SED1530's can easily configure a large display having the high flexibility with very few data transmission restriction. The microprocessor writes and reads data to/from the RAM through I/O buffer. As LCD controller operates independently, data can be written into RAM at the same time as data is being displayed, without causing the LCD to flicker.

Display data RAM

Display on LCD

## 7.7. Output Status Selector

The SED1530 series except SED1531 can set a COM output scan direction to reduce restrictions at LCD module assembly. This scan direction is set by setting "1" or "0" in the output status register D3.Fig.5 shows the status.

#### Fig.5 shows the status.

| LCD output   |     | 00              |                           |                | O131    |  |  |  |

|--------------|-----|-----------------|---------------------------|----------------|---------|--|--|--|

| ADC          | "0" | 0 (H)→          | Column oddrogg            | Column oddrood |         |  |  |  |

| (D0)         | "1" | 83(H) <b></b> ← | Column address<br>83(H) ← |                |         |  |  |  |

|              |     |                 | Display data RAM          |                |         |  |  |  |

|              | D3  |                 |                           |                |         |  |  |  |

| SED1530D0*   | 0   |                 | SEG100                    | СОМ0           | COM31   |  |  |  |

| 1 SED1330D0* |     |                 | SEG100                    | СОМ31СОМ0      |         |  |  |  |

| SED1530DA*   | 0   | COM150          | SEG100                    |                | COM1631 |  |  |  |

| SED1530DF*   | 1   | COM1631 SEG100  |                           |                | COM150  |  |  |  |

#### Relationship between display data RAM and addresses (if initial display line is 1CH):

|                                        | Code |    |    |         |      |         |         |                 |               |          |        |                                                                                                                                    |

|----------------------------------------|------|----|----|---------|------|---------|---------|-----------------|---------------|----------|--------|------------------------------------------------------------------------------------------------------------------------------------|

| Command                                | A0   | RD | WR | D7      | D6   | D5      | D4      | D3              | D2            | D1       | D0     | Function                                                                                                                           |

| (1)Display ON/OFF                      | 0    | 1  | 0  | 1       | 0    | 1       | 0       | 1               | 1             | 1        | 0      | Turns on LCD panel when goes                                                                                                       |

|                                        |      |    |    |         |      |         |         |                 |               |          | 1      | high, and turns off when goes low.                                                                                                 |

| (2)Initial Display Line                | 0    | 1  | 0  | 0       | 1    | Start o | display | addres          | s             |          |        | Specifies RAM display line for COM0.                                                                                               |

| (3)Set page Address                    | 0    | 1  | 0  | 1       | 0    | 1       | 1       | Page a          | address       |          |        | Sets the display RAM page in Page<br>Address register.                                                                             |

| (4)Set column<br>Address 4 higher bits | 0    | 1  | 0  | 0       | 0    | 0       | 1       | Highe<br>addres | r Colui<br>ss | nn       |        | Sets 4 high bits of column address of display RAM in register.                                                                     |

| (4)Set column<br>Address 4 higher bits | 0    | 1  | 0  | 0       | 0    | 0       | 0       | Lower<br>addres | r Colun<br>ss | nn       |        | Sets 4 lower bits of column address of display RAM in register.                                                                    |

| (5)Read Status                         | 0    | 0  | 1  | Status  |      |         |         | 0               | 0             | 0        | 0      | Reads the sets information.                                                                                                        |

| (6)Write Display Data                  | 1    | 1  | 0  | Write   | data |         |         |                 |               |          | •      | Writes data in display RAM.                                                                                                        |

| (7) Read Display Data                  | 1    | 0  | 1  | Read of | data |         |         |                 |               |          |        | Read data from display RAM.                                                                                                        |

| (8)ADC Select                          | 0    | 1  | 0  | 1       | 0    | 1       | 0       | 0               | 0             | 0        | 0<br>1 | Sets normal relationship between<br>RAM column address and segment<br>driver when low, but reverses the<br>relationship when high. |

| (9)Normal/Reverse Display              | 0    | 1  | 0  | 1       | 0    | 1       | 0       | 0               | 1             | 1        | 0      | Normal indication when low, but full indication when high.                                                                         |

| (10)Entire Display ON/OFF              | 0    | 1  | 0  | 1       | 0    | 1       | 0       | 0               | 1             | 0        | 0      | Selects normal display(0) or<br>Entire Display ON (1).                                                                             |

| (11)Set LCD Bias                       | 0    | 1  | 0  | 1       | 0    | 1       | 0       | 0               | 0             | 1        | 0      | Sets LCD drive voltage bias ratio.                                                                                                 |

| (12)Read-Modify-Write                  | 0    | 1  | 0  | 1       | 1    | 1       | 0       | 0               | 0             | 0        | 0      | Increments Column Address<br>counter during each write when<br>high and during each read when<br>low.                              |

| (13)End                                | 0    | 1  | 0  | 1       | 1    | 1       | 0       | 1               | 1             | 1        | 0      | Releases the Read-Modify-Write.                                                                                                    |

| (14)Reset                              | 0    | 1  | 0  | 1       | 1    | 1       | 0       | 0               | 0             | 1        | 0      | Resets internal functions.                                                                                                         |

| (15) Set Output Status<br>Register     | 0    | 1  | 0  | 1       | 1    | 0       | 0       | 0               | *             | *        | *      | Selects COM output scan direction. *Invalid data                                                                                   |

| (16) Set Power Control                 | 0    | 1  | 0  | 0       | 0    | 1       | 0       | 1               | Opera         | tion sta | itus   | Selects the power circuit operation mode.                                                                                          |

| (17)Set Electronic Control<br>Register | 0    | 1  | 0  | 1       | 0    | 0       | Electr  | onic co         | ontrol v      | alue     |        | Sets V5 output voltage to Electronic control register.                                                                             |

| (18)Set Standby                        | 0    | 1  | 0  | 1       | 0    | 1       | 0       | 1               | 1             | 0        | 0      | Selects standby status.<br>0:OFF 1:ON                                                                                              |

| (19) Power Save                        | -    | -  | -  | -       | -    | -       | -       | -               | -             | -        | -      | Compound command of display<br>OFF and entire display ON                                                                           |

| (20)Test Command                       | 0    | 1  | 0  | 1       | 1    | 1       | 1       | *               | *             | *        | *      | IC Test command Do not use!                                                                                                        |

Note: Do not use any other command, or the system malfunction may result.

# 8. QUALITY ASSURANCE

## 8.1 Test Condition

8.1.1 Temperature and Humidity(Ambient Temperature)

| Temperature | : | $20 \pm 5^{\circ}C$   |

|-------------|---|-----------------------|

| Humidity    | : | $65 \pm \mathbf{5\%}$ |

8.1.2 Operation

Unless specified otherwise, test will be conducted with LCM in operation.

8.1.3 Container

Unless specified otherwise, vibration test will be conducted on module only.

8.1.4 Test Frequency Single cycle.

### 8.1.5 Test Method

| No. | Parameter                                | Conditions                                                                                                                                | Regulations |

|-----|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| 1   | High Temperature Operating               | 50 ± 2 °C                                                                                                                                 | Note 3      |

| 2   | Low Temperature Operating                | 0 ± 2 °C                                                                                                                                  | Note 3      |

| 3   | High Temperature Storage                 | 70 ± 2 °C                                                                                                                                 | Note 3      |

| 4   | Low Temperature Storage                  | -20 ± 2 °C                                                                                                                                | Note 3      |

| 5   | Vibration Test<br>(Non-operation state)  | Total fixed amplitude : 1.5mm<br>Vibration Frequency : 10 ~ 55Hz<br>One cycle 60 seconds to 3 directions<br>of X.Y.Z. for each 15 minutes | Note 3      |

| 6   | Damp Proof Test<br>(Non-operation state) | 40°C ± 2°C, 90~95%RH, 96h                                                                                                                 | Note 1,2    |

| 7   | Shock Test<br>(Non-operation state)      | To be measured after dropping from<br>60cm high once concrete surface in<br>packing state                                                 | Note 3      |

Note 1: Returned under normal temperature and humidity for 4 hours.

Note 2: No dew condensation to be observed.

Note 3: No change on display and in operation under the test condition

Confidential Document

## 8.2 Inspection condition

8.2.1 Inspection conditions

The LCD shall be inspected under 40W white fluorescent light.

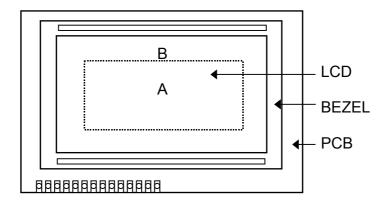

8.2.2 Definition of applicable Zones

A : Display Area

B : Non-Display Area

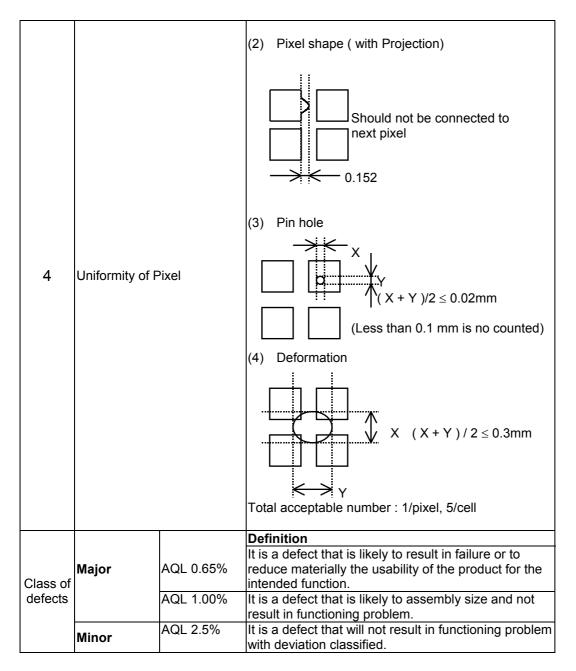

## 8.2.3 Inspection Parameters

| No | . Parameter                                | Criteria                                                                                                                                                                                                                                                                                                                                 |

|----|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1  | Black or White spots                       | $\begin{array}{ c c c c c }\hline \hline Zone & Acceptable & Class & AQL \\ \hline Dimension & A & B & Defects & \\ \hline D < 0.15 & * & * & \\ \hline 0.15 \le D < 0.2 & 4 & 4 & \\ \hline 0.2 \le D \le 0.25 & 2 & 2 & \\ \hline D \le 0.3 & 0 & 1 & \\ \hline \hline D = (Long + Short) / 2 & * : Disregard & \\ \hline \end{array}$ |

| 2  | Scratch, Substances                        | $\begin{tabular}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                 |

| 3  | Air Bubbles<br>(between glass & polarizer) | $\begin{tabular}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                 |

| 4  | Uniformity of Pixel                        | (1) Pixel shape (with Dent)<br>0.152                                                                                                                                                                                                                                                                                                     |

## 8.3 Sampling Condition

Unless otherwise agree in written, the sampling inspection shall be applied to the incoming inspection of customer. Lot size: Quantity of shipment lot per model. Sampling type: normal inspection, single sampling Inspection level: Level II Sampling table: MIL-STD-105E Confidential Document

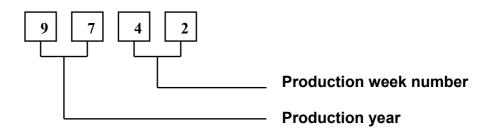

# 9. LOT NUMBERING SYSTEM

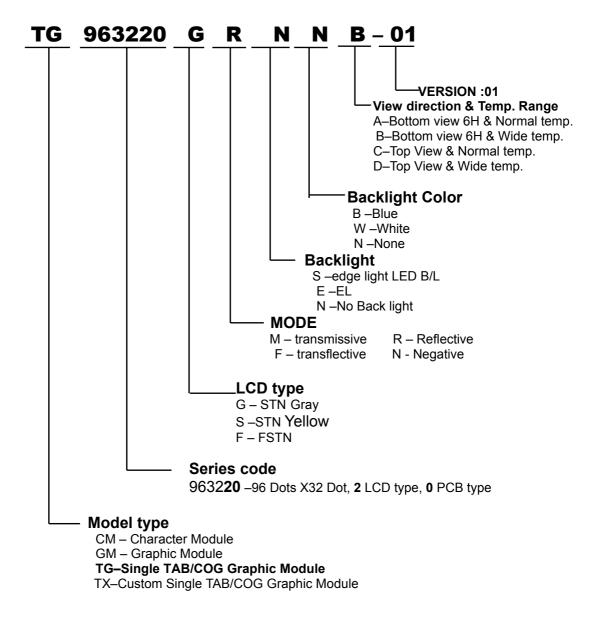

## 10. LCM NUMBERING SYSTEM

# 11. PRECAUTION FOR USING LCM

#### 1. LIQUID CRYSTAL DISPLAY (LCD)

LCD is made up of glass, organic sealant, organic fluid, and polymer based polarizers. The following precautions should be taken when handing,

(1). Keep the temperature within range of use and storage. Excessive temperature and humidity could cause

polarization degredation, polarizer peel off or bubble.

(2). Do not contact the exposed polarizers with anything harder than an HB pencil lead. To clean dust off the display surface, wipe gently with cotton, chamois or other soft material soaked in petroleum benzin.

(3). Wipe off saliva or water drops immediately. Contact with water over a long period of time may cause polarizer deformation or color fading, while an active LCD with water condensation on its surface will cause corrosion of ITO electrodes.

(4). Glass can be easily chipped or cracked from rough handling, especially at corners and edges.

(5). Do not drive LCD with DC voltage.

2. Liquid Crystal Display Modules

2.1 Mechanical Considerations

LCM are assembled and adjusted with a high degree of precision. Avoid excessive shocks and do not make any alterations or modifications. The following should be noted. (1). Do not tamper in any way with the tabs on the metal frame.

(2). Do not modify the PCB by drilling extra holes, changing its outline, moving its components or modifying its pattern.

(3). Do not touch the elastomer connector, especially insert an backlight panel (for example, EL).

(4). When mounting a LCM make sure that the PCB is not under any stress such as bending or twisting . Elastomer contacts are very delicate and missing pixels could result from slight dislocation of any of the elements.

(5). Avoid pressing on the metal bezel, otherwise the elastomer connector could be deformed and lose contact, resulting in missing pixels.

#### 2.2. Static Electricity

LCM contains CMOS LSI's and the same precaution for such devices should apply, namely

(1). The operator should be grounded whenever he/she comes into contact with the module. Never touch any of the conductive parts such as the LSI pads, the copper leads on the PCB and the interface terminals with any parts of the human body.

(2). The modules should be kept in antistatic bags or other containers resistant to static for storage.

(3). Only properly grounded soldering irons should be used.

(4). If an electric screwdriver is used, it should be well grounded and shielded from commutator sparks.

(5) The normal static prevention measures should be observed for work clothes and working benches; for the latter conductive (rubber) mat is recommended.(6). Since dry air is inductive to static, a relative humidity of 50-60% is recommended.

#### 2.3 Soldering

(1). Solder only to the I/O terminals.

(2). Use only soldering irons with proper grounding and no leakage.

(3). Soldering temperature :  $280^{\circ}C \pm 10^{\circ}C$

(4). Soldering time: 3 to 4 sec.

(5). Use eutectic solder with resin flux fill.

(6). If flux is used, the LCD surface should be covered to avoid flux spatters. Flux residue should be removed after wards.

#### 2.4 Operation

(1). The viewing angle can be adjusted by varying the LCD driving voltage V0.

(2). Driving voltage should be kept within specified range; excess voltage shortens display life.

(3). Response time increases with decrease in temperature.

(4). Display may turn black or dark blue at temperatures above its operational range; this is (however not pressing on the viewing area) may cause the segments to appear "fractured".

(5). Mechanical disturbance during operation (such as pressing on the viewing area) may cause the segments to appear "fractured".

#### 2.5 Storage

If any fluid leaks out of a damaged glass cell, wash off any human part that comes into contact with soap and water. Never swallow the fluid. The toxicity is extremely low but caution should be exercised at all the time.

#### 2.6 Limited Warranty

Unless otherwise agreed between DATA IMAGE and customer, DATA IMAGE will replace or repair any of its LCD and LCM which is found to be defective electrically and visually when inspected in accordance with DATA IMAGE acceptance standards, for a period on one year from date of shipment. Confirmation of such date shall be based on freight documents. The warranty liability of DATA IMAGE is limited to repair and/or replacement on the terms set forth above. DATA IMAGE will not responsible for any subsequent or consequential events.

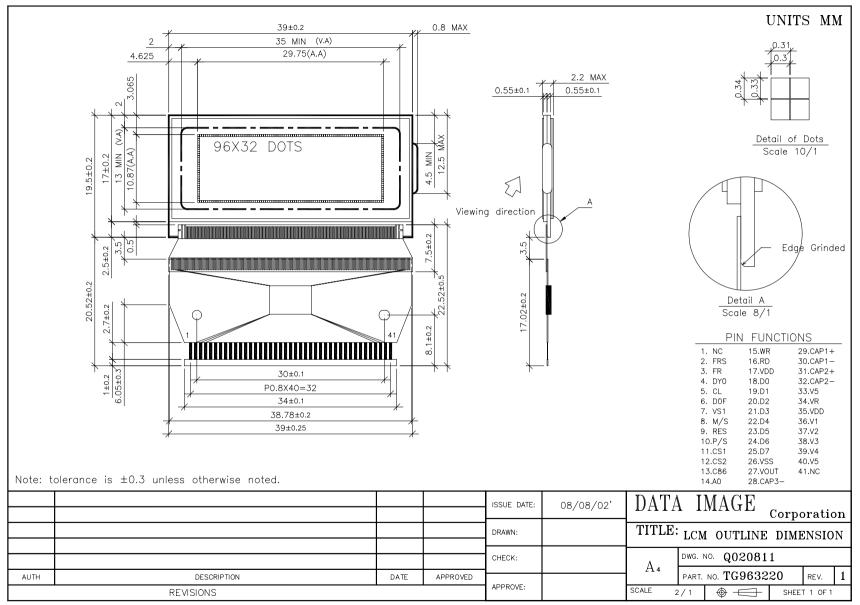

# **13. PACKAGE INFORMATION**

.ge: 27 /27